FPGA deployment and scaling made simple

Chris Kachris chris@inaccel.com

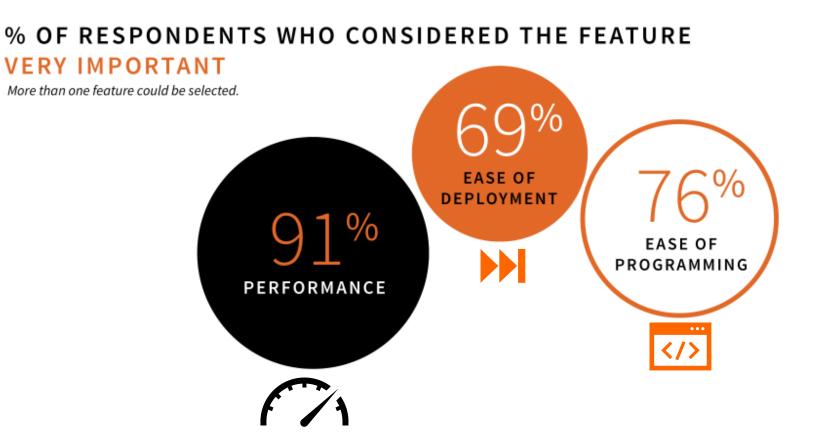

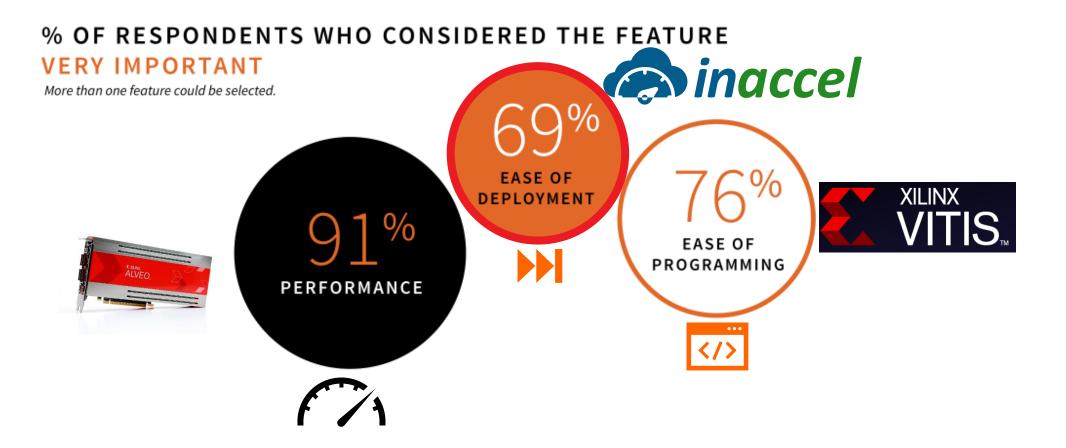

### What software developers want

Source: Databricks, Apache Spark Survey 2016, Report

### What software developers want

Source: Databricks, Apache Spark Survey 2016, Report

# *inaccel* mission

> Help companies speedup their applications by using accelerators (FPGAs) seamlessly

> How?

**Unique InAccel FPGA orchestrator**

Automated deployment, scaling and management of FPGA clusters

···· </>

••••

### Main challenges of FPGAs

*maccel*

# **InAccel Products (Accelerators as IP)**

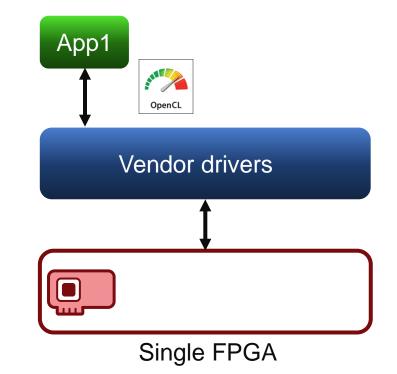

# **Current limitations for FPGA deployment**

- > Currently only one application can talk to a single FPGA accelerator through OpenCL

- > Application can talk to a **single** FPGA.

- > Complex device sharing

- From multiple threads/processes

- Even from the same thread

- > Explicit allocation of the resources (memory/compute units)

- > User need to specify which FPGA to use (device ID, etc.)

### From single instance to data centers

</>

···· </>

*inaccel*

- > Easy deployment

- > Instant scaling

- > Seamless sharing

- > Multiple-users

- > Multiple applications

- > Isolation

- > Privacy

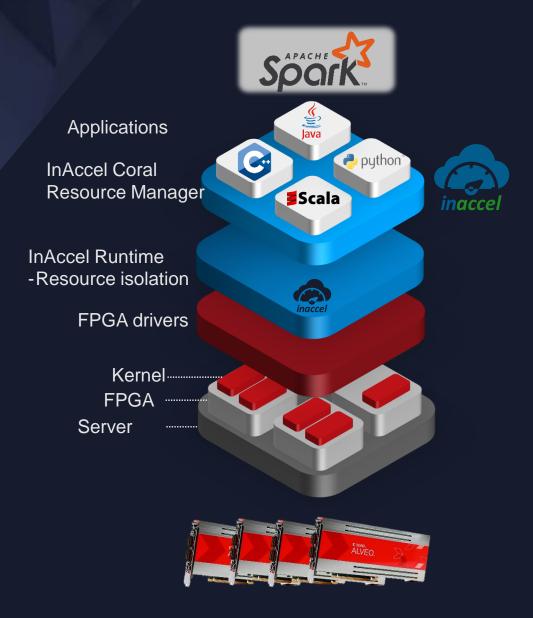

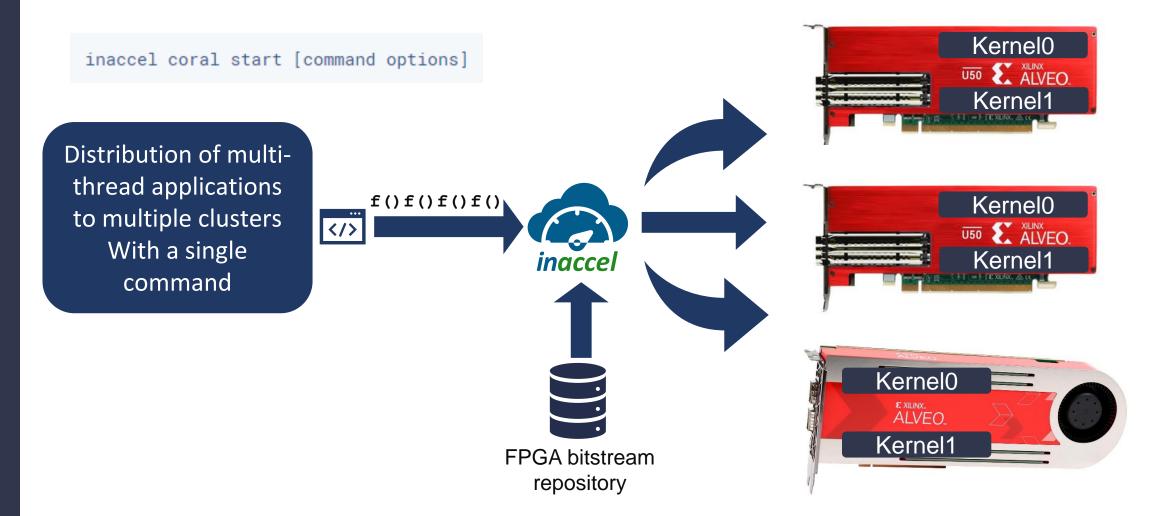

# Scalable Orchestrator for FPGA clusters contracted

### Automated Deployment, Scaling and Management of FPGA clusters

Seamless invoking from C/C++, Python, Java and Scala. No need for OpenCL

Automatic configuration and management of the FPGA **bitstreams** and memory

Seamless **sharing** of the FPGA cluster from multiple threads/processes/applications/users

Fully **scalable**: Scale-up (multiple FPGAs per node) and Scale-out (multiple FPGA-based servers over Spark)

© Copyright 2019 InAccel

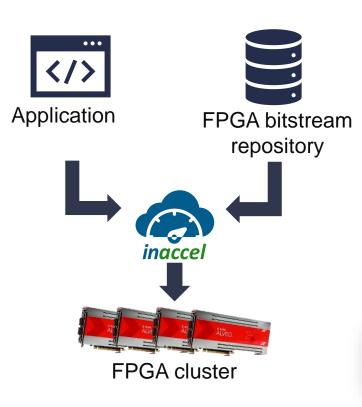

# **FPGA** bitstream repository

> FPGA Resource Manager is  $\bigcirc$ integrated with Jfrog n bitstream repository that is used to store FPGA bitstreams

### 🝙 inaccel

#### Artifact Repository Browser

| Tree Simple Q                                               |      | T.    |

|-------------------------------------------------------------|------|-------|

| ∨ ♥ bitstreams                                              |      |       |

| — > 🖻 intel                                                 |      |       |

| - ∨ 🖾 xilinx                                                |      |       |

| — > 🖻 aws-vu9p-f1-04261818/dynamic_5.0/com                  |      |       |

| — V 🖾 u200                                                  |      |       |

| — 🗸 🖻 xdma_201820.1/com                                     |      |       |

| — ∨ 🖾 inaccel/ml                                            |      |       |

| > 🖾 ALS/1.0/4Solver                                         |      |       |

| — > 🖾 KMeans/1.0                                            |      |       |

| → 🗁 LogisticRegression/1.0/4Gradients                       |      |       |

| — ∨ 🖾 xilinx/vision/0.1                                     |      |       |

| — > 🖾 2Affine_4Convolve                                     |      |       |

| > 🗇 2Affine_4EdgeDetection                                  |      |       |

| → 🗁 xdma_201830.2/com/xilinx/vitis                          |      |       |

| — > 🖻 dataCompression/lz4/1.0                               |      |       |

| — > 🖻 quantitativeFinance                                   |      |       |

| — > 🖻 security/aes256/1.0                                   |      |       |

| > 🗇 vision/1.0/1stereoBM                                    |      |       |

|                                                             |      |       |

| — > ▷ inaccel/ml/LogisticRegression/1.0/4Gradients          |      |       |

| ✓ ☎ xilinx/vitis/quantitativeFinance/monteCarlo/1.0/1Calibr | atio | on_1F |

| 🗟 bitstream.json                                            |      |       |

| MCAE_k.xclbin                                               |      |       |

inaccel bitstream install [command options]

### Single command

| 🖻 vision/1.0/1stere    | eoBM                                                                          |

|------------------------|-------------------------------------------------------------------------------|

| General                | Properties 🚖                                                                  |

| Info                   |                                                                               |

| Name:                  | 1stereoBM 🗍                                                                   |

| Repository Path:       | bitstreams/xilinx/u200/xdma_201830.2/com/xilinx/vitis/vision/1.0/1stereoBM/ 🗍 |

| Deployed By:           | inaccel                                                                       |

| Artifact Count / Size: | Show                                                                          |

| Created:               | 05-12-19 13:39:52 +00:00 (40d 20h 10m 24s ago)                                |

|                        |                                                                               |

### https://store.inaccel.com

# **FPGA repository - artifact**

$\times$

| 🔊 inaccel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                     | bitstream.json                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Artifact Repository Browser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| Tree Simple Q 🚖 🍸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 🖻 vision/1.0/1stereoBM              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>4</b> 1 |

| O bitstreams     D intel     D intel     D xilinx     D avs-vu9p-f1-04261818/dynamic_5.0/com     D v200     D v dxdma_201820.1/com     D lacs(1/n)     D ALS(1,0/450/ver     D LogisticRegression/1.0/4Gradients     D X linx/vision/0.1     D D ALS(1,0/450/ver     D X linx/vision/0.1     D D ALS(1,0/450/ver     D V xilinx/vision/0.1     D D D ALS(1,0/450/ver     D D D ALS(1,0/450/ver     D V xilinx/vision/0.1     D D D D D D D D D D D D D D D D D | General     Properties ★       Info | <pre>1 { 2 "name": "krnl_stereopipeline.xclbin", 3 "bitstreamId": "com.xilinx.vitis.vision", 4 "version": "1.0", 5 "description": "Xilinx Vitis Stereo Block Matching Accelerator", 6 "platform": { 7 "vendor": "xilinx", 8 "name": "u200", 9 "version": "xdma_201830.2" 10 }, 11 "kernels": [{ 12 "name": [ 13 "stereopipeline_accel" 14 ], 15 "kernelId": "stereoBM", 16 "arguments": [{ 17 "type": "ap_uint&lt;32&gt;*", 18 "name": "img_L", 19 "access": "n"</pre> |            |

| > Artifact: JSON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | l file + bitstream                  | 20 },                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

21

22

23

24

25

26

27

28

{

},

"type": "ap\_uint<32>\*",

"type": "ap\_uint<32>\*",

"name": "img\_disp",

"name": "img\_R",

"access": "r"

### Artifact: JSON file + bitstreau

- >> Vendor

- >> FPGA cards

- >> Version

- >> Kernels

- >> Arguments

| www.inaccel.com™ |  |

|------------------|--|

# **FPGA repository CLI**

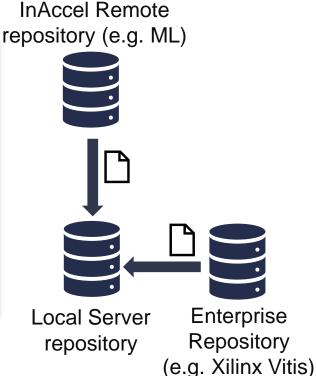

- > Simple CLI interface for the local repository

- > Local repository can fetch artifacts from external links (e.g. Xilinx or InAccel repository) with proprietary artifacts

| Command                   | Description                                                                                                 | reposi |

|---------------------------|-------------------------------------------------------------------------------------------------------------|--------|

| inaccel bitstream decrypt | Decrypt an FPGA binary                                                                                      |        |

| inaccel bitstream encrypt | Encrypt an FPGA binary                                                                                      |        |

| inaccel bitstream parse   | Parse FPGA binary build-metadata                                                                            |        |

| inaccel bitstream install | Install a bitstream to the local or a remote repository, from a local or a remote source                    |        |

| inaccel bitstream list    | List all the bitstreams or detailed information for specific bitstreams in the local or a remote repository |        |

| inaccel bitstream remove  | Remove one or more bitstreams from the local or a remote repository                                         |        |

# **Compatible with any Xilinx Vitis libraries**

### Generality

# > Build your own repository of accelerators.

InAccel provides a stack of cores including Machine Learning. You can combine all these libraries, along with your own ones, seamlessly in the same application.

### > Test it with any Xilinx Vitis/SDAccel example

InAccel Documentation Overview Accelerators ~ FPGA Resource Manager ~ Getting Started Deploying Accelerators API Docs ~ Programming Guides Examples Seamless Integration ~ About ~

#### automatically scale your accelerated solutions using in-house or 3rd-party accelerators, from high-level programming languages.

#### 1. Prerequisites

- Docker Community Edition (CE)

- FPGA Runtime (Intel or Xilinx)

- Git | OpenJDK (Java Development Kit) 8 | Maven

- OpenCV 3.4.2

#### 👌 Amazon F1

Find InAccel Default Image, equipped with all the required development tools (and many more), available free on EC2 Community AMIs section.

#### 2. Download InAccel

git clone https://bitbucket.org/inaccel/release.git inaccel && cd inaccel

#### **Computer Vision**

#### Acknowledgements:

The Computer vision accelerators (FPGA bitstreams/kernels) used for the purposes of this demonstation are written by developers at Xilinx.

Resources:

• SDAccel Examples - Vision

https://docs.inaccel.com/latest/manager/examples/

# Simple invoking, deployment

# No need for OpenCL

No need to allocate buffers No need to specify bitstreams No need to program specific device

inaccel::Request add\_req {"com.inaccel.math.vector.addition"}; add\_req.Arg(a).Arg(b).Arg(c).Arg(size); inaccel::Coral::Submit(add\_req);

- Much simpler invoking

- Software-alike function invoking

- No need for OpenCL directives

- Same API for C/C++, Java, Python

- Native API

```

std::cout << "Device[" << i << "]: program successful!\n";

OCL CHECK(err, krnl vector add = cl::kernel(orogram. "vadd

```

```

OCL_CHECK(err, krnl_vector_add = cl::Kernel(program, "vadd", &err));

valid_device++;

```

www.inaccel.com™

std::string binaryFile = argv[1];

// Allocate Memory in Host Memory

// Create the test data

for (int i = 0; i < DATA\_SIZE; i++) {</pre>

auto devices = xcl::get xil devices();

// and will return the pointer to file buffer.

auto fileBuf = xcl::read\_binary\_file(binaryFile);

for (unsigned int i = 0; i < devices.size(); i++) {</pre>

q = cl::CommandQueue(

std::cout << "Trying to program device[" << i

source\_hw\_results[i] = 0;

// OPENCL HOST CODE AREA START

int valid\_device = 0;

OCL\_CHECK(err,

OCL CHECK(err,

} else {

if (err != CL\_SUCCESS) {

auto device = devices[i];

cl\_int err; cl::Context context; cl::Kernel krnl\_vector\_add; cl::CommandQueue q;

size\_t vector\_size\_bytes = sizeof(int) \* DATA\_SIZE;

std::vector<int, aligned\_allocator<int>> source\_in1(DATA\_SIZE); std::vector<int, aligned\_allocator<int>> source\_in2(DATA\_SIZE); std::vector<int, aligned\_allocator<int>> source\_hw\_results(DATA\_SIZE); std::vector<int, aligned\_allocator<int>> source\_sw\_results(DATA\_SIZE);

std::generate(source\_in1.begin(), source\_in1.end(), std::rand); std::generate(source\_in2.begin(), source\_in2.end(), std::rand);

source\_sw\_results[i] = source\_in1[i] + source\_in2[i];

// get\_xil\_devices() is a utility API which will find the xilinx

cl::Program::Binaries bins{{fileBuf.data(), fileBuf.size()}};

// Creating Context and Command Queue for selected Device

OCL\_CHECK(err, context = cl::Context({device}, NULL, NULL, &err));

context, {device}, CL\_QUEUE\_PROFILING\_ENABLE, &err));

<< "]: " << device.getInfo<CL\_DEVICE\_NAME>() << std::endl;

cl::Program program(context, {device}, bins, NULL, &err));

// platforms and will return list of devices connected to Xilinx platform

// read\_binary\_file() is a utility API which will load the binaryFile

// When creating a buffer with user pointer (CL\_MEM\_USE\_HOST\_PTR), under the hood user ptr // is used if it is properly aligned. when not aligned, runtime had no choice but to create // its own host side buffer. So it is recommended to use this allocator if user wish to

// create buffer using CL\_MEM\_USE\_HOST\_PTR to align user buffer to page boundary. It will

// ensure that user buffer is used when user create Buffer/Mem object with CL\_MEM\_USE\_HOST\_PTR

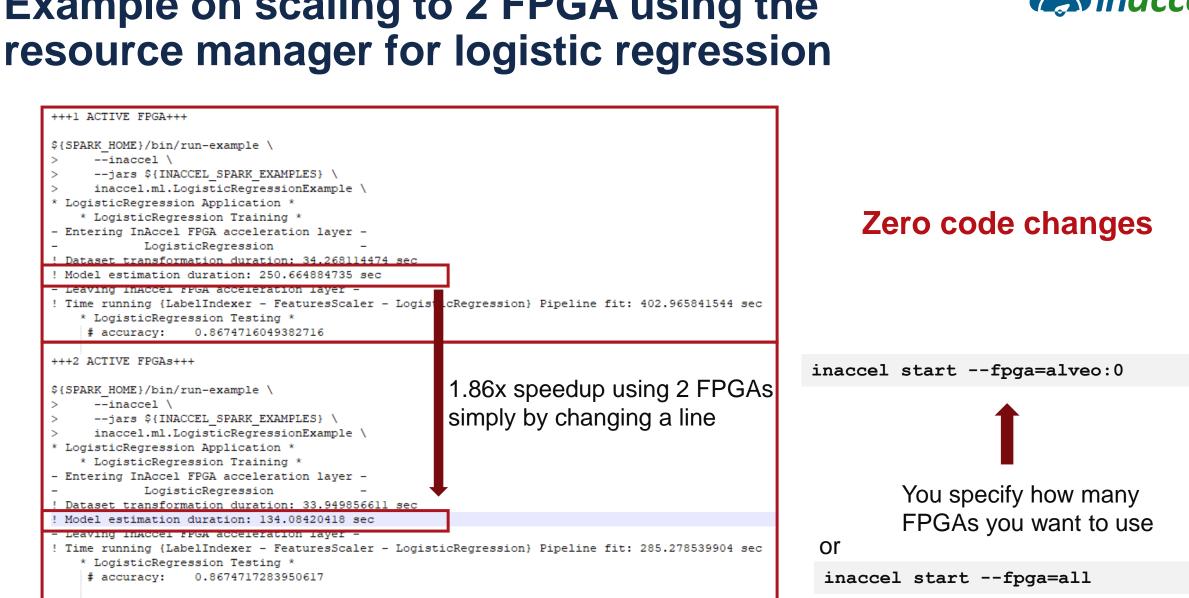

# **Instant scaling**

# **Example on scaling to 2 FPGA using the**

### **Instant Scalability**

### > Instant scalability to

- >> Multiple kernels

- >> Multiple FPGAs in the same server

- >> Multiple servers (using Kubernetes)

inaccel start --fpga=xilinx:0,xilinx:1

Lower than 2x speedup is due to the lower clock rate and PCI conflicts

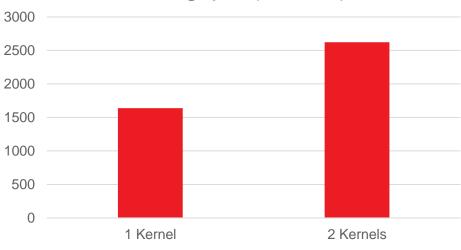

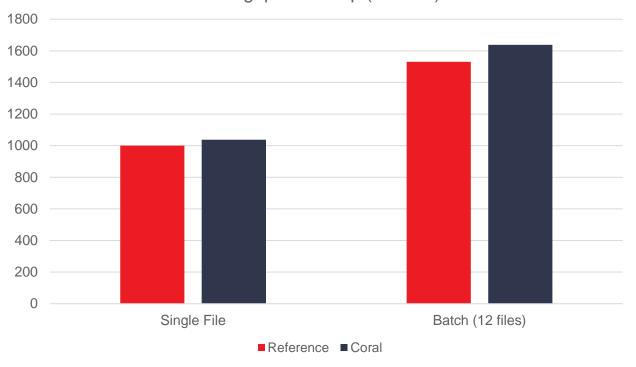

### Throughput (MB/sec)

# Zero overhead, Improved Throughput

#### Throughput for Gzip (MB/sec)

### **Optimized Pipeline**

> No need for OpenCL event to synchronize pipeline execution

### > Instant pipeline using InAccel FPGA manager => Optimized pipeline

- >> Higher Throughput

- >> Simplified code (no need for OpenCL events, barriers)

- >> Useful for multiple kernels, multiple threads/applications

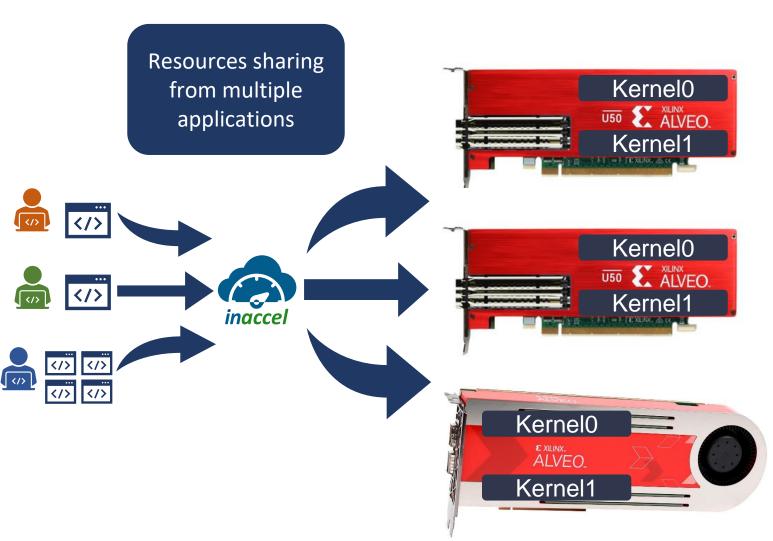

### **Seamless sharing of the resources**

Utilization from:

- Multiple threads

- Multiple processes

- Multiple applications

- Multiple users

- Multiple **containers**

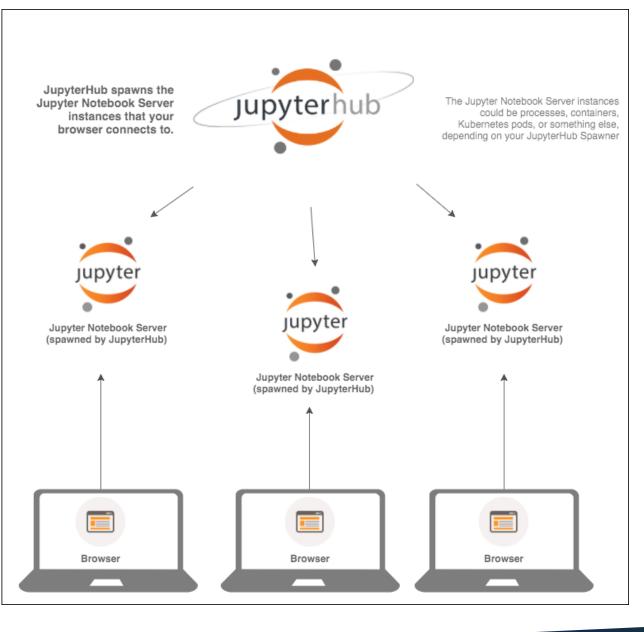

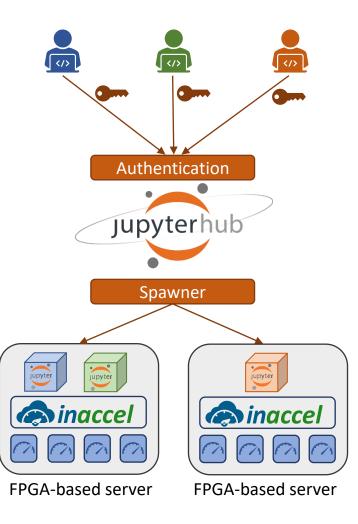

# **Jupyter - JupyterHub**

Deploy and run your FPGA-accelerated applications using Jupyter Notebooks

InAccel manager allows the instant deployment of FPGAs through JupyterHub

### **JupyterHub on FPGAs**

- Instant acceleration of Jupyter Notebooks with zero code-changes

- > Offload the most computationally intensive tasks on FPGA-based servers

Help

▼ ■ ■

Streaming

InAccel - Spark Spark

spark = SparkSession.builder.config(conf=conf).appName("LogisticRegressionExample").getOrCreate()

C jupyter LogisticRegressionExample

Insert

MLlib Pipeline

This notebook shows h

You can read more abc

In [ ]: from pyspark.sql import SparkSession

Kernel

Interrupt

Restart

Cell

N Run

Widgets

Restart & Clear Output

Restart & Run All

Reconnect Shutdown

Change kernel

For this example we'll be using the Extended Modified NIST (National Institute of Standards and Technology) Letters dataset which is a set of handwritten letters derived from the NIST Special Database 19 and converted to a 28x28 pixel grayscale image format. The dataset merges a balanced set of the uppercase and lowercase letters into a single 26-class task. Further information on the dataset contents and conversion process can be found in the paper available at https://arxiv.org/abs/1702.05373v1

e on historic data and apply it to streaming data.

Logout

InAccel - Spark O

Trusted

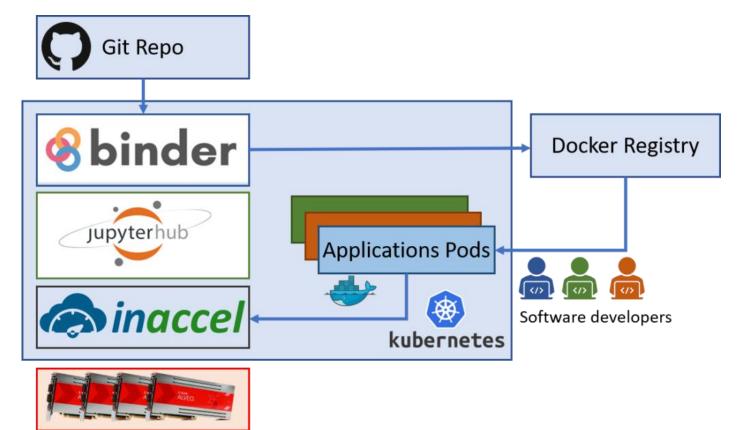

### **BinderHub on FPGAs**

- BinderHub enables an end user to easily specify a desired computing environment from a Git repo

- InAccel integration allows users to accelerate their applications from git repo using remote FPGA-based accelerators

**FPGA-based Server**

https://inaccel.com/deploying-fpgas-from-git-repos-instantly-using-binderhub/

# **Unique FPGA monitoring tool**

# **FPGA** monitoring tool

### > Utilization of the kernels

- >> Time to read from DDR

- >> Time to execute

- >> Time to write back in DDR

### > Useful for performance optimization

- > Support for multiple kernels, multiple FPGA cards

- > Integrated with Coral FPGA manager

# **FPGA Manager deployment**

### Easy to Deploy

- > Launch a container with InAccel's Docker image or even deploy it as a daemonset on a Kubernetes cluster and enjoy acceleration services at the drop of a hat.

- > https://hub.docker.com/u/inaccel/

| docker hub | Q Search for great content (e.g., mysql)                                                                       | Explore        | Pricing | Sign In | Sign Up |

|------------|----------------------------------------------------------------------------------------------------------------|----------------|---------|---------|---------|

|            | inaccel Edit profile<br>Community Organization III InAccel & https://inaccel.com/ O Joined November 12, 2018   |                |         |         |         |

|            | Repositories                                                                                                   |                |         |         |         |

|            | Displaying 6 of 6 repositories                                                                                 |                |         |         |         |

|            | inaccel/coral-free<br>By inaccel • Updated 32 minutes ago<br>InAccel FPGA Resource Manager   Free<br>Container | 27<br>Download |         |         |         |

- Easy deployment

- Easy scalability

- Easy integration

# **Compatibility with Xilinx Ecosystem**

### > FPGA repository for the Vitis Library

ALVEO. U200

Pre-compiled bitstreams for all Vitis Library for Alveo family cards (U50, U200, U250, U280)

ALVEO. U250

Scaling of Vitis libraries to multiple kernels, multiple Alveo cards, AWS f1.4x, f1.16x

ALVEO, U280

ALVEO, U50

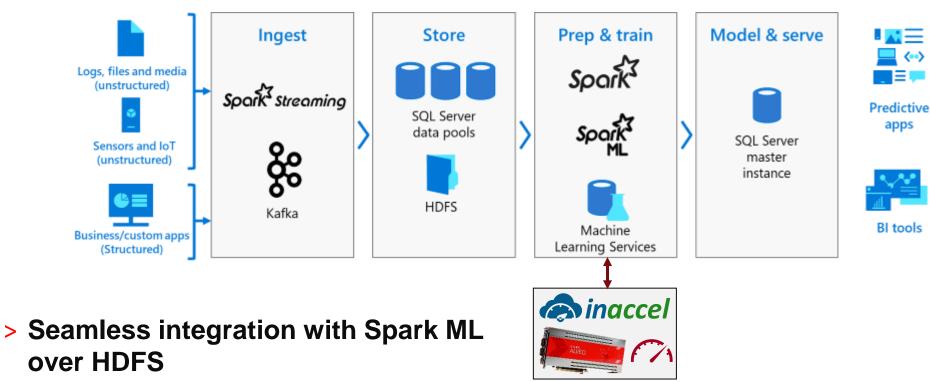

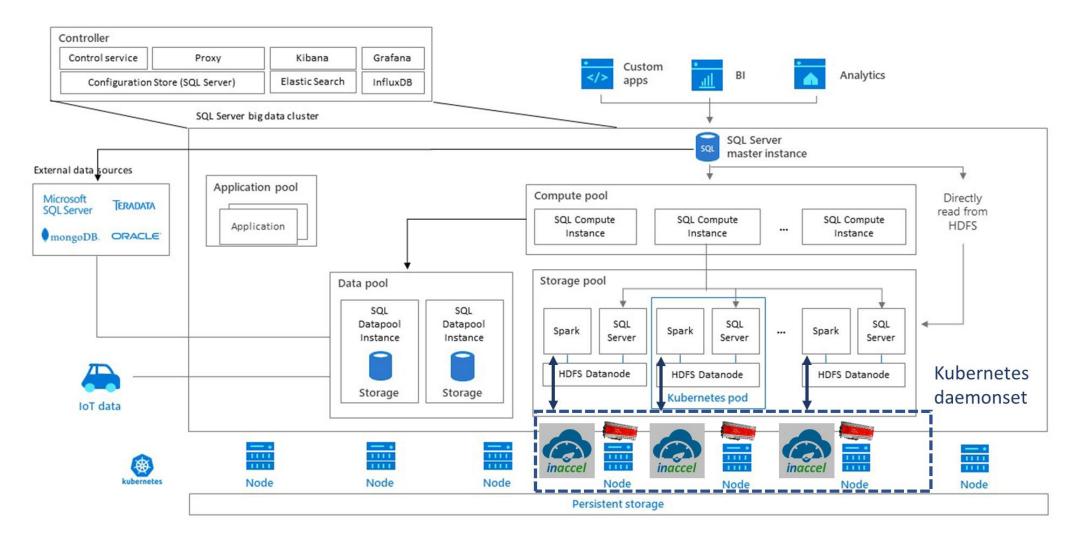

### Accelerated ML on top of SQL 2019

- >> Zero Code changes

- >> Higher Performance

- >> Lower OpEx

### https://www.youtube.com/watch?v=qu7ct\_4CknM

https://medium.com/@inaccel/accelerated-spark-ml-using-fpgas-on-top-of-microsoft-sql-server-2019-big-data-cluster-88acc130d780

### Integration with SQL Big Data Cluster 2019

https://medium.com/@inaccel/accelerated-spark-ml-using-fpgas-on-top-of-microsoft-sql-server-2019-big-data-cluster-88acc130d780

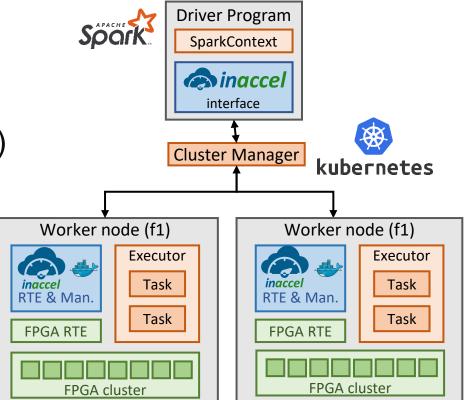

### InAccel's Coral manager integrated with Spark

- > Integrated solution that allows

- >> Scale Up (1, 2, or 8 FPGAs per node)

- >> Scale Out to multiple nodes (using Spark API)

- >> Seamless integration

- >> Docker-based deployment

- >> No-need to specify which FPGA to use

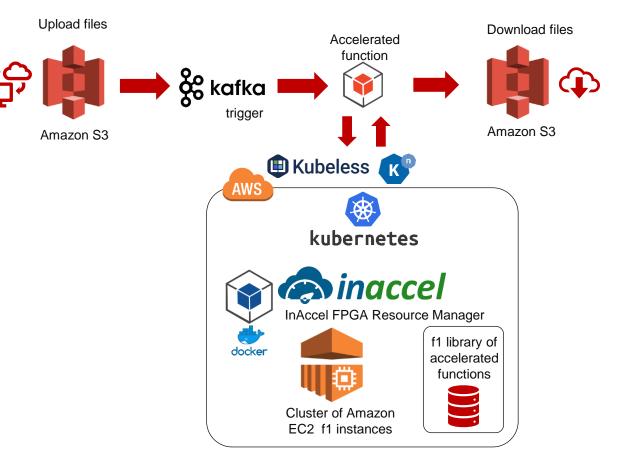

# **Serverless deployment**

*contraction in accel*

- Integrated framework for serverless deployment

- > Compatible with Kubernetes

- > Compatible with Kubeless, Knative

- > Users only have to upload the images on the S3 bucket and then InAccel's FPGA Manager automatically deploy the cluster of FPGAs, process the data and then store back the results on the S3 bucket.

- > Users do not have to know anything about the FPGA execution.

https://medium.com/@inaccel/fpgas-goes-serverless-on-kubernetes-55c1d39c5e30

### **Runtime specification**

> The InAccel Coral runtime specification aims to specify the configuration, and execution interface for the efficient management of any accelerator-based hardware resource.

### > Hook Developers

> Hook developers can extend the functionality of a compliant runtime by hooking into an accelerator's lifecycle with an external application. Example use cases include sophisticated hardware configuration, advanced logging, IP licensing (hardware identification - authentication - decryption), etc.

### > Platform Developers

> Platform developers can build runtime implementations that expose diverse hardware resources and system configuration, containing low-level OS and hardware-specific details, on a particular platform.

https://github.com/InAccel/runtime

# **Pricing model (enterprise version)**

**FPGA** Resource manager

- > Pricing model per node (server)

- > Each node can have 1 to 8 FPGAs

| FPGA Resource manager | 20 servers or less | More than 20 servers |

|-----------------------|--------------------|----------------------|

| Monthly               | \$300/servers      | \$250/server         |

| Yearly                | \$3,000/server     | \$2,500/server       |

# **Successful Use cases, Integrations**

**E** XILINX.

MEMBER

**ALLIANCE PROGRAM**

### Registered Technology Partner

### **Partnerships**

FPGA Design Solutions Network **intel**

**Azure**

### Making FPGA-based acceleration easy

info@inaccel.com

www.inaccel.com