University

Easy sharing of FPGAs for Universities

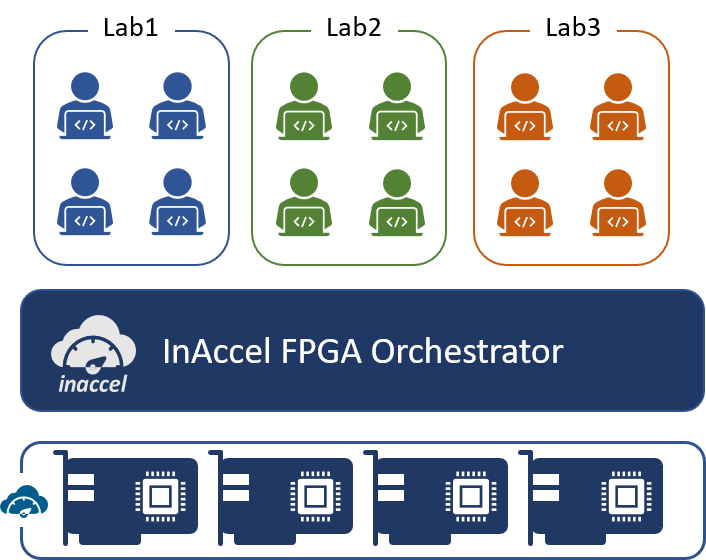

How do you allow multiple students to share the available FPGAs?

Many universities have limited number of FPGA cards that want to share with multiple students.

InAccel FPGA orchestrator allows multiple students to share one or more FPGAs seamlessly.

It allows students to just invoke the function that want to accelerate and InAccel FPGA manager performs the serialization and the scheduling of the functions to the available FPGA resources.

Even if each student or group uses a different bitstream, InAccel orchestrator manages the configuration of the bitstreams.

Fully compatible with Xilinx Alveo cards (U50, U200, U250, U280) and Intel PAC cards. InAccel support even heterogeneous deployments (different Alveo or PAC cards).

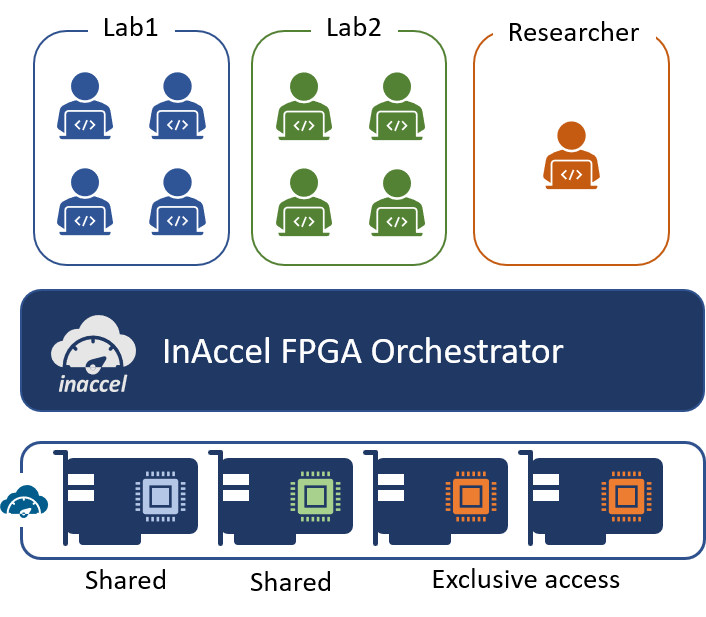

But the researchers want exclusive access

InAccel orchestrator allows to select which FPGA cards will be available for multiple students and which FPGAs can be allocated exclusively to researchers and Ph.D. students (so they can get accurate measurements for their papers).

The FPGAs that are shared with multiple students will perform on a best-effort approach (InAccel manager performs the serialization of the requested access) while the researchers have exclusive access to the FPGAs with zero overhead.

Also researchers can see how their applications scale to multiple FPGAs as InAccel support automatic scaling.

InAccel orchestrator allows easy deployment with simple function invoking from C/C++, Python and Java.

It also comes along with several tutorials and lab exercises.

Ready to use Lab exercises

InAccel has prepared lab exercises that show how students can accelerate their function on FPGAs on their premises or on cloud.

It includes example for multiple applications like

- Machine Learning

- Vision

- Compression

- Encryption

It is fully compatible with Xilinx Vitis libraries and the Xilinx Adaptive Compute Clusters (XACC)

Get started

Simple step-by-step guide on how to install and run InAccel

Create a license for free